摘要:通过研究数字交换芯片的组成结构,将数字交换芯片进行了模块化的分割,根据技术指标,利用FPGA 技术分别设计了时钟生成模块、数据发送模块、数据接收模块以及微处理器接口模块,最终根据数字交换芯片的“交换模式”与“消息模式”的工作原理对所设计的各个模块进行了组合,完成了数字交换芯片的设计。测试结果表明:基于FPGA 技术设计的数字交换芯片实现了“交换模式”与“消息模式”的功能;并且达到了技术指标的要求,实现了32 条母线输入和32 条母线输出,每条母线输入数据速率与输出数据速率为8.192 Mb/s,通道容量为4 096×4 096 的无阻塞交换。利用FPGA 技术设计了一种数字交换芯片,采用FPGA 芯片实现了数字交换芯片的功能。对于数字交换芯片,实现了自主可控,所设计的数字交换芯片满足国内调度通信对数字交换芯片的需求,而且用软件设计替代了硬件设计,可以适应技术指标的改变。

关键词:数字交换芯片;FPGA;调度通信;模块设计;功能测试;无阻塞交换

0 引言

数字交换芯片是程控数字交换机中的关键性器件,主要实现数字交换的功能。但是我国数字交换芯片主要依赖于国外进口,随着时间的推移,可能会面临国外厂家停产或停供的风险,随着国内用户需求的改变也会要求技术指标变化,依靠从国外进口难以及时满足国内需求。因此,研究一种满足国内需求的数字交换芯片,实现数字交换芯片的自主可控很有必要。

数字交换芯片是实现数字交换网络的一种体现,而数字交换网络是程控数字交换机的核心部分,主要实现时隙的交换。数字交换芯片的发展与数字交换网络密切相关,数字交换网络可以是时间接线器,或者是空间接线器[1⁃2],目前有成熟的大规模集成电路,为了扩大交换网容量,由时间接线器和空间接线器可以组成大规模的数字交换网络,用来完成不同母线与不同时隙上的数据交换。与此同时,大规模集成电路与工艺的发展已经可将包括串并转换、并串转换和时间接线器与空间接线器的级联形式TST 数字交换网络集成到一块大规模集成电路上,形成数字交换芯片。为了满足不同的技术需求,数字交换芯片种类繁多,主要区别在于输入输出母线数量、输入输出速率以及交换容量。然而,数字交换芯片的本质就是实现“交换模式”与“消息模式”。其中“交换模式”指的是数字交换芯片与微处理器协同工作,实现时隙的无阻塞交换;“消息模式”指的是微处理器能控制读出数字交换芯片中的输入数据,也能将写入数字交换芯片中的数据进行输出。每个公司生产的数字交换芯片内部结构可能有所差异,但功能基本相同。MITEL 公司推出的一系列数字交换芯片,以其优良的性价比成为数字交换芯片中的佼佼者。

基于FPGA 技术设计数字交换芯片,在程控数字交换机中实现“交换模式”与“消息模式”。设计的数字交换芯片指标要求为:32 条输入输出母线,输入输出数据流达到8.192 Mb/s,通道容量达到4 096×4 096 通道的无阻塞交换。本文首先分析了数字交换芯片的组成结构与工作原理以及FPGA 技术的特点。其次根据FPGA技术开发的特点,对数字交换芯片进行模块化划分,根据本文数字交换芯片的指标要求,设计数字交换芯片结构框图,利用FPGA 技术设计数字交换芯片的各个组合模块,用Modelsim 软件进行仿真验证,分析信号的波形是否达到了本文的技术指标。最后,根据数字交换芯片的工作原理对各个组合模块进行合并,完成数字交换芯片的设计[3⁃4]。

1 数字交换芯片组成结构分析

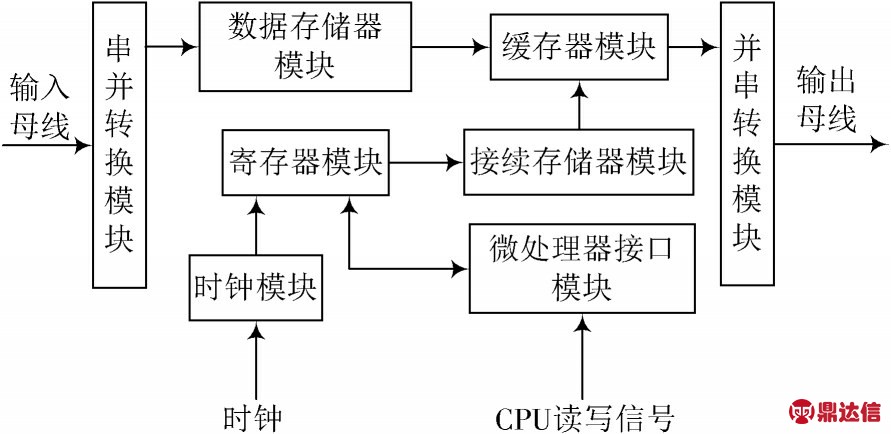

数字交换芯片是将串并转换、数字交换网络、并串转换集成在一起形成的产品,由于E1 接口处理的是串行数据,数字交换网络处理的是并行数据,所以数字交换芯片接收端需要将串行数据转换为并行数据,数字交换芯片发送端需要将并行数据转换为串行数据,而实现业务上面的功能是在数字交换网络中完成。如图1所示,数字交换芯片的组合电路包括串并转换模块、数据存储器模块、缓存器模块、寄存器模块、接续存储器模块、时钟模块、微处理器模块以及并串转换模块。本文根据数字交换芯片中“交换模式”与“消息模式”的工作机制,分析数字交换芯片各个组成电路之间的工作机制。

图1 数字交换芯片组成结构

“交换模式”的工作思路为:串行PCM 编码数据经过串并转换,按照母线号与时隙号固定存入数据存储器模块的相应单元内;寄存器模块通过微处理器接口模块接收来自微处理器的信号,并将此信号写到接续存储器模块;再将接续存储器中的内容作为数据存储器的地址,以某种顺序读出,接着写入缓存器模块,经过并串转换模块,将时隙交换后的串行PCM 编码数据输出,从而实现数字交换的目的。

“消息模式”的工作思路为:“消息模式”分为“微处理器接收模式”与“微处理器发送模式”。“微处理器接收模式”指串行PCM 编码数据经过串并转换,按照母线号与时隙号固定存入数据存储器模块的相应单元内;微处理器将数据存储器模块中的数据读出。“微处理器发送模式”是指微处理器直接将数据写入数字交换芯片中的接续存储器模块,读出接续存储器模块中的数据,写入缓存器模块、经过并串转换,以串行PCM 编码数据输出。有时需要将二者结合起来,微处理器先读取数字交换芯片中接收的数据,再写入特定的数据到数字交换芯片中进行发送。

2 FPGA 技术分析

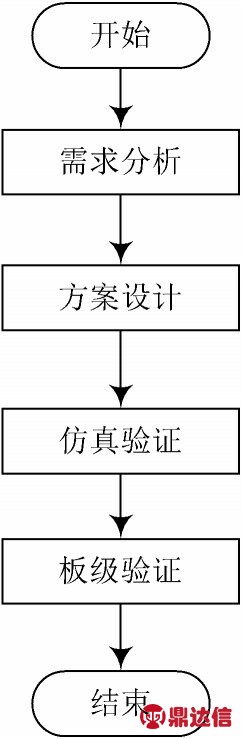

基于FPGA 技术设计数字交换芯片是进行产品的设计,而不是设计FPGA 芯片,主要是利用FPGA 技术进行数字交换芯片功能的设计[5⁃6]。FPGA 芯片中有丰富的IP 核提供给开发者使用,可以满足数字交换芯片中的时钟问题以及RAM 存储的问题,并且FPGA 芯片有大量的引脚,可以解决数字芯片引脚数量的问题,满足数字交换芯片的设计需求。利用FPGA 技术设计电路,用户不需要进行流片就能得到合适的选择,而且FPGA芯片是小批量生产的最佳选择之一。如图2 所示,FPGA 开发过程一般是根据需求分析进行方案的设计,用硬件描述语言设计具体的功能[7],用仿真器进行仿真验证,最后烧录至芯片中进行硬件测试[8]。本文目的是提供一种设计方法,因此只介绍了仿真验证。

图2 FPGA 设计流程图

3 FPGA 的数字交换芯片设计与仿真分析

本文在Altera 公司提供的Quartus 开发平台上进行设计,使用第三方工具Modelsim 软件对所设计的数字交换芯片进行仿真[9⁃10],分析了数字交换芯片基本组合电路的功能与工作原理。基于FPGA 技术设计数字交换芯片必须结合本文的技术指标,将数字交换芯片进行模块化分割,模块的合理分割会降低开发过程中的复杂度。将数字交换芯片划分为4 个模块,分别为时钟生成模块、数据接收模块、数据发送模块以及CPU 接口模块。

利用FPGA 技术对这4 个模块进行相应的方案设计,每个模块的功能利用硬件描述语言进行设计与仿真。完成这4 个模块的设计之后,按照“交换模式”与“消息模式”的思想,将时钟生成模块,数据接收模块,数据发送模块以及微处理器接口模块进行组合,完成数字交换芯片的设计。

3.1 FPGA 设计数字交换芯片的组成结构

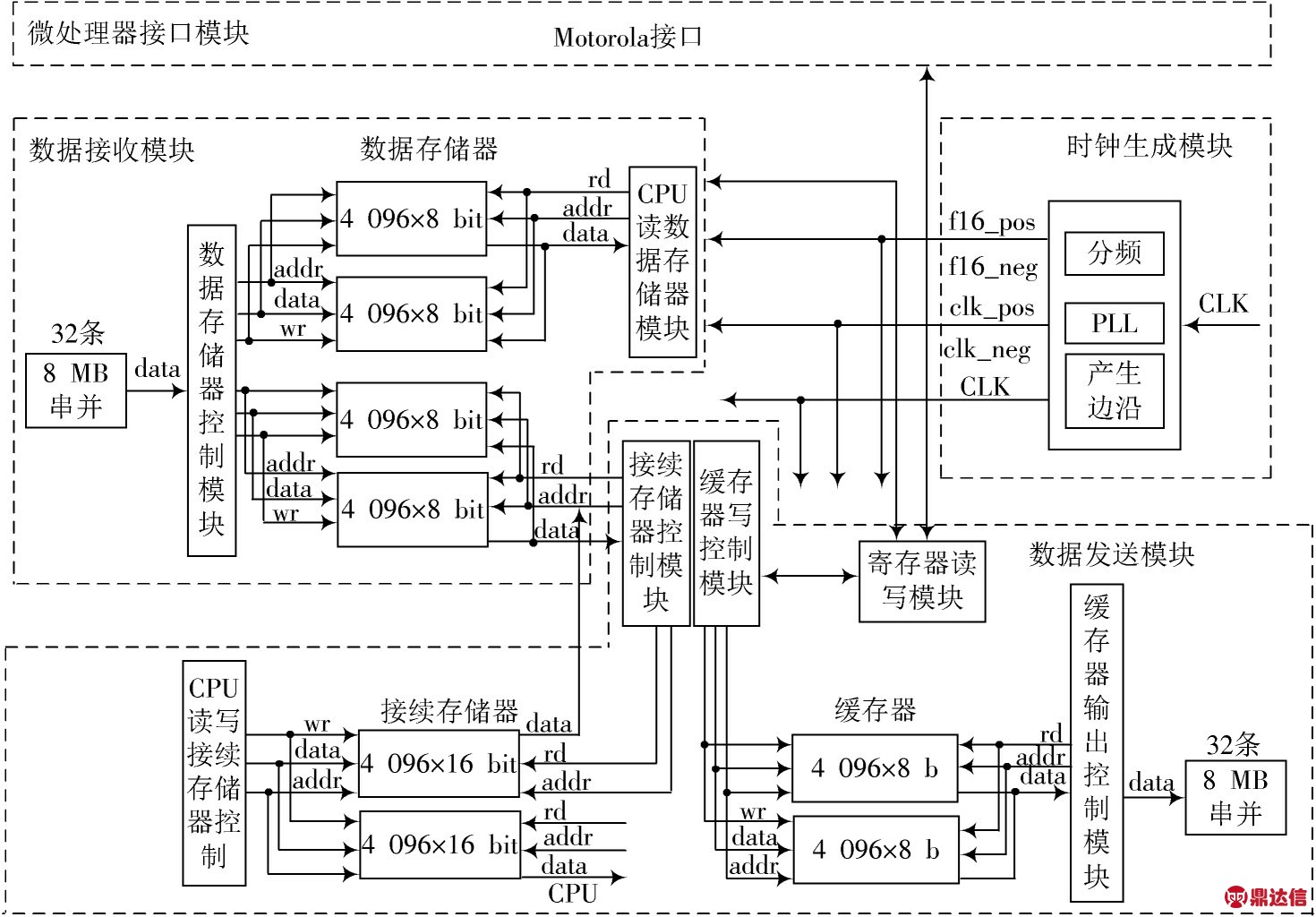

文中分析了数字交换芯片的基本组合电路与工作原理,用FPGA 逻辑模块设计相应的数字交换芯片电路组成模块,实现FPGA 数字交换芯片的设计[11],如图3 所示。下文将详细介绍数字交换芯片各个模块的设计思路与仿真结果。

3.2 时钟生成模块

3.2.1 时钟生成模块的设计思路

如图3 所示,时钟生成模块主要为整个系统提供具体的时钟,供应整个系统正常工作。本文设计的输入输出母线数据为8.192 Mb/s,时钟信号为16.384 MHz 与帧同步信号f16。首先Testbench 产生时钟16.384 MHz驱动整个工程,通过IP 核PLL 倍频为主频需要的98.304 MHz;帧同步信号f16 的周期为125 μs,输入时钟16.384 MHz 周期大约为61 ns,125 μs/61 ns=2 048。因此,利用计数器产生2 048 个数据,用输入信号16.384 MHz 产生帧同步信号f16;另外需要对输入信号16.384 MHz 与帧同步信号f16 进行边沿采集,将16.384 MHz 延迟2 拍,会得到2 个中间延迟信号,用与非的关系就可以得到16.384 MHz 与帧同步信号f16 的上升沿信号与下降沿信号。

图3 FPGA 设计数字交换芯片的组成结构

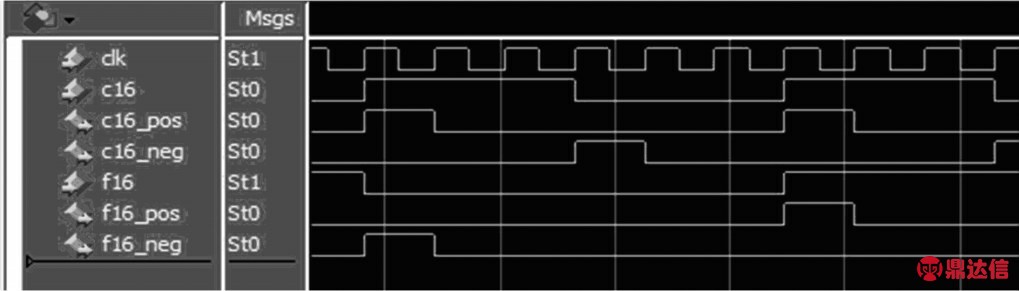

3.2.2 时钟生成模块的仿真结果

图4 时钟生成模块仿真波形表明,clk 是98.304 MHz时钟频率,c16 是16.384 MHz 的时钟频率,f16 是帧同步信号,c16_pos 与c16_neg 分别对应c16 的上升沿与下降沿,f16_pos 与f16_neg 分别对应f16 的上升沿与下降沿,各个时钟信号达到了预期的期望。

图4 时钟生成模块仿真图

3.3 数据接收模块

3.3.1 数据接收模块的设计思路

如图3 所示,数据接收模块主要由3 个子模块构成,分别为32 条母线串并转换模块、数据存储器控制模块以及数据存储器模块。

本文的设计指标为32 条母线,每条母线输入数据的速率为8.192 Mb/s。根据E1接口标准,速率为8.192 Mb/s时,每条母线一帧总共有128 个时隙,因为有32 条母线并且每条母线速率8.192 Mb/s,因此数据存储器的RAM深度应该选择4 096,经过串并转换生成的并行码是8 bit,因此RAM 的宽度应该选择8 bit。

分析“交换模式”与“消息模式”的工作机制,为了实现RAM 的读操作与写操作写相互独立,采用乒乓操作读写方式[12],“交换模式”与“消息模式”分别需要2 个RAM。

3.3.2 数据接收模块的仿真结果

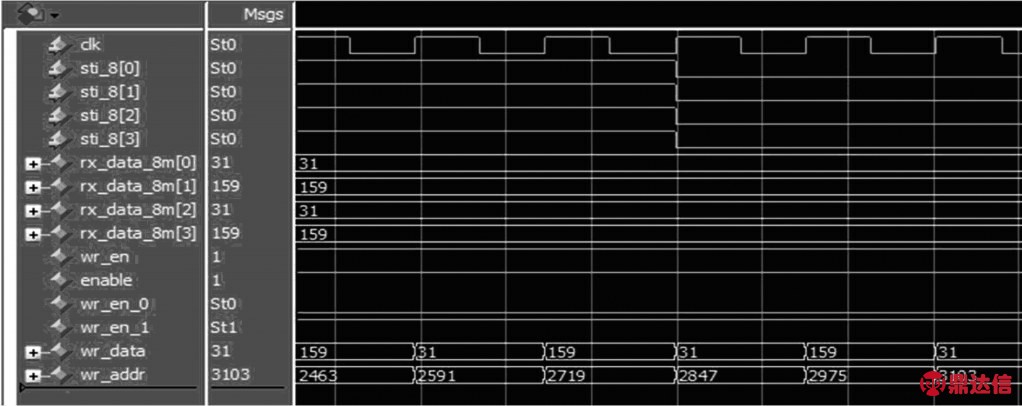

由图5 数据接收模块仿真波形可知,为了便于观察,32 条母线数据由2 种不同的串行数据循环得到,这里只显示前4 条母线数据,即sti_8[0],sti_8[1],sti_8[2],sti_8[3],其余28 条依次类推;32 条母线数据经过串并转换后,转换为并行码rx_data_8m[0],rx_data_8m[1],rx_data_8m[2],rx_data_8m[3],按地址addr_ram 信号进行排序,每条母线间隔128 bit,保证每条母线上的同一个时隙,同时写入4 096×8 bit的RAM。

图5 数据接收模块仿真图

3.4 数据发送模块

3.4.1 数据发送模块的设计思路

如图3 所示数据发送模块设计思路,数据发送模块主要由寄存器模块、接续存储器模块、接续存储器控制模块、缓存器写控制模块、缓存器模块、缓存器输出控制模块以及32 条母线并串转换模块组成。相应地,32 条母线中每条母线一帧总共有128 个时隙,因此接续存储器的RAM 深度应该选择4 096,接续存储器RAM 的位宽包含功能选择,因此接续存储器的RAM 宽度应该选择16 bit,分为高8 bit 与低8 bit。分析“交换模式”与“消息模式”的工作机制,接续存储器由2 个16×4 096 容量的RAM 组成。微处理器对两个接续存储器写操作相同,一个接续存储器用来完成“交换模式”和“消息模式”;另一个接续存储器由微处理器控制进行读操作,目的是验证微处理器写入的指令与读出的指令是否相同。

3.4.2 数据发送模块的仿真结果

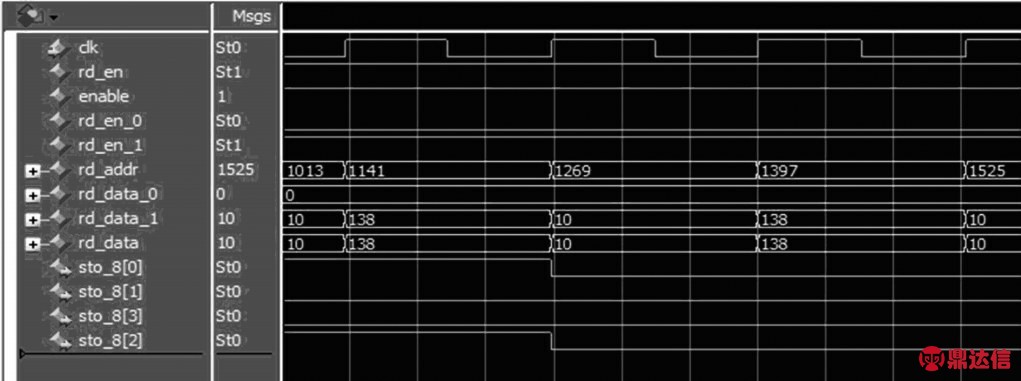

如图6 所示,由仿真波形可知,在数据发送模块,rd_en 读控制信号与enable 控制信号产生相应的rd_en_0 读控制信号和rd_en_1 读控制信号,按rd_addr 的顺序将缓存器RAM 中8 bit 并行数据乒乓操作读出,产生rd_data_0 信号与rd_data_1信号,将rd_data_0信号与rd_data_1 信号赋值给rd_data,最终经过并串转换,将并行数据转换为串行数据进行发送。

图6 数据发送模块仿真图

3.5 微处理器接口模块

3.5.1 微处理器接口模块的设计思路

如图3 所示,微处理器接口模块的目的是实现CPU与数字交换芯片的通信,CPU 写指令配合数字交换芯片[13],使其工作在“交换模式”或者“消息模式”。

3.5.2 微处理器接口模块的仿真结果

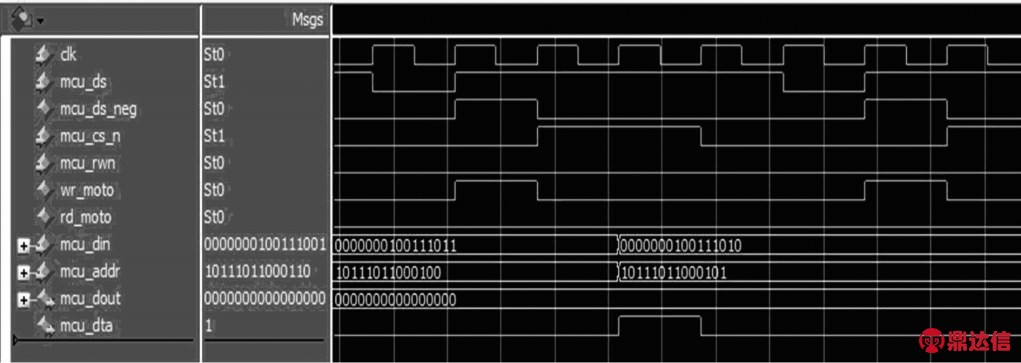

如图7 所示,由仿真波形可知:

图7 微处理器接口模块仿真图

mcu_ds 信号与mcu_cs_n 信号同时有效时作为控制信号;

mcu_cs_n 是片选信号;

mcu_rwn 是微处理器的读写使能信号;

mcu_din 是写入数据信号;

mcu_dout 是读出数据信号,控制微处理器对数字交换芯片的读写操作。

3.6 数字交换芯片的功能仿真

3.6.1 交换模式的仿真结果

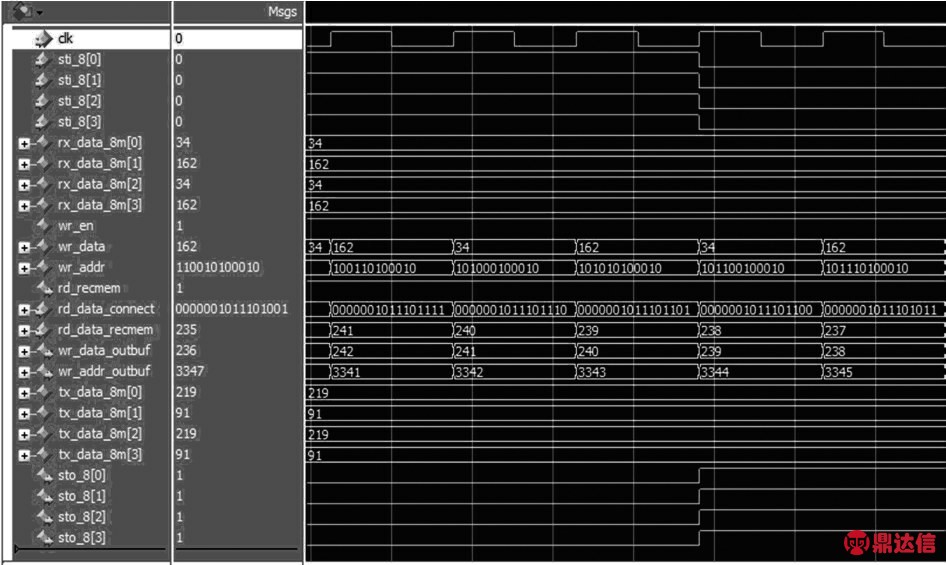

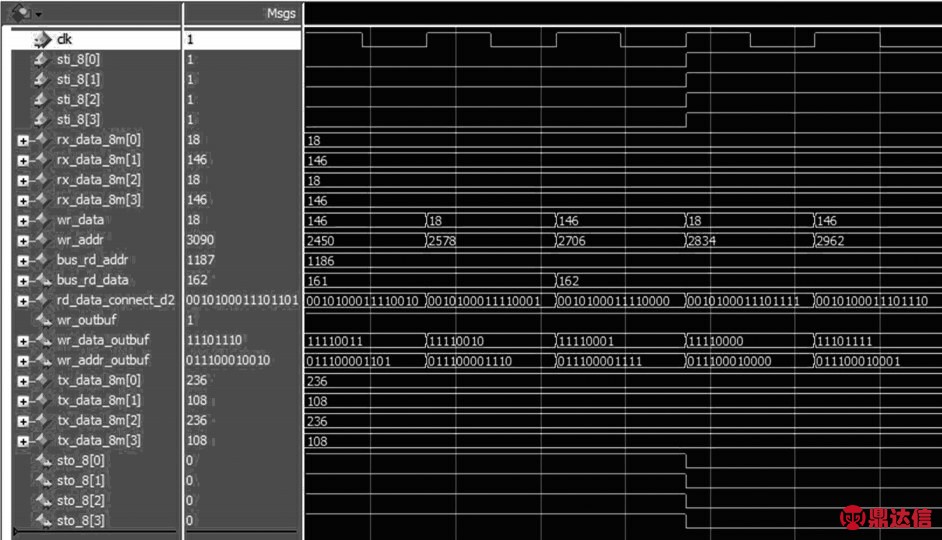

如图8 所示,交换模式仿真结果表明:

图8 交换模式仿真图

输入串行数据sti_8[0],sti_8[1],sti_8[2],sti_8[3],经过串并转换,转换为并行数据rx_data_8m[0],rx_data_8m[1],rx_data_8m[2],rx_data_8m[3],按顺序赋值给wr_data,然后wr_data 写入数据存储器RAM;

读出接续存储中的数据rd_data_connect[11:0]作为数据存储器的地址端,然后按顺序读出数据存储器,实现时隙的交换;

交换之后的数据rd_data_recmem 写入发送模块wr_data_outbuf,发送模块将交换之后的数据按顺序读出tx_data_8m[0],tx_data_8m[1],tx_data_8m[2],tx_data_8m[3],最终转换为串行数据sto_8[0],sto_8[1],sto_8[2],sto_8[3]进行发送,完成时隙的交换。

3.6.2 消息模式的仿真结果

如图9 所示,消息模式的仿真波形表明:

图9 消息模式仿真图

输入串行数据sti_8[0],sti_8[1],sti_8[2],sti_8[3]经过串并转换,转换为并行数据rx_data_8m[0],rx_data_8m[1],rx_data_8m[2],rx_data_8m[3],按赋值给顺序wr_data写入数据存储器RAM 之中,bus_rd_data 将数据存储器中的数据读出,完成了消息模式中的“微处理器接收模式”;

rd_data_connect的低8位数据送到了wr_data_outbuf 信号端,按顺序读出tx_data_8m[0],tx_data_8m[1],tx_data_8m[2],tx_data_8m[3],最终转换为串行数据sto_8[0],sto_8[1],sto_8[2],sto_8[3]进行发送,完成了消息模式中的“微处理器发送模式”。

4 结语

本文设计数字交换芯片的目的是利用FPGA 技术设计数字交换芯片的功能,实现“交换模式”与“消息模式”,满足国内的市场需求,摆脱对外国公司的依赖并实现自主可控。在FPGA 芯片与数字交换专有芯片同时满足需求的情况下,FPGA 芯片的成本低于数字专有芯片的价格,并且可以重复利用。最后数字交换芯片本质为实现“交换模式”与“消息模式”,但因速率与通道容量不同且种类繁多,本文利用FPGA 设计数字交换芯片,把电路设计转化为软件设计,实现了相应的技术指标,也可以根据实际需求的变化,做出相应的设计,而不需要改动PCB板子,提高了数字交换芯片的扩展性,使其更好地满足程控数字交换机对数字交换芯片技术指标的要求。